วันที่ 26 สิงหาคม 2568 สำนักงานการวิจัยแห่งชาติ (วช.) กระทรวงการอุดมศึกษา วิทยาศาสตร์ วิจัยและนวัตกรรม ร่วมกับ มหาวิทยาลัยเกษตรศาสตร์ จัดการอบรมเชิงปฏิบัติการ “Analog IC Design with Cadence” ภายใต้การดำเนินงานศูนย์รวมผู้เชี่ยวชาญด้านการออกแบบไมโครอิเล็กทรอนิกส์ประเทศไทย โดย ดร.วิภารัตน์ ดีอ่อง ผู้อำนวยการสำนักงานการวิจัยแห่งชาติ ได้มอบหมายให้ นางสุภาพร โชคเฉลิมวงศ์ ผู้อำนวยการกองบริหารทุนวิจัยและนวัตกรรม 1 (วช.) เป็นประธานกล่าวเปิดงาน และ ผู้ช่วยศาสตราจารย์ ดร.อุไรวรรณ อินต๊ะถา เลขาคณะทำงานศูนย์รวมผู้เชี่ยวชาญด้านการออกแบบไมโครอิเล็กทรอนิกส์ประเทศไทย กล่าวต้อนรับ พร้อมด้วยนักวิจัย คณาจารย์ ผู้ประกอบการ และภาคีเครือข่ายทั้งภาครัฐและเอกชน เข้าร่วมการอบรม ณ ห้องคอมพิวเตอร์ 506 อาคารสำนักวิทยาการคอมพิวเตอร์ มหาวิทยาลัยเกษตรศาสตร์

นางสุภาพร โชคเฉลิมวงศ์ กล่าวว่า อุตสาหกรรมไมโครอิเล็กทรอนิกส์ถือเป็นโครงสร้างพื้นฐานสำคัญที่ขับเคลื่อนประเทศและกำหนดทิศทางนวัตกรรมในหลายสาขา ไม่ว่าจะเป็นพลังงานอัจฉริยะ ยานยนต์ไฟฟ้า การแพทย์ หรือเทคโนโลยีดิจิทัลและ AI ซึ่งล้วนต้องอาศัยวงจรอนาล็อกเป็นหัวใจหลัก การสร้างบุคลากรที่มีความเชี่ยวชาญในการออกแบบวงจรอนาล็อก จึงเป็นการดำเนินงานที่ วช. ให้ความสำคัญ เพื่อเพิ่มขีดความสามารถในการแข่งขันของประเทศอย่างยั่งยืน

ผู้ช่วยศาสตราจารย์ ดร.อุไรวรรณ อินต๊ะถา กล่าวว่า ศูนย์รวมผู้เชี่ยวชาญด้านการออกแบบไมโครอิเล็กทรอนิกส์ประเทศไทย เล็งเห็นถึงความสำคัญในการพัฒนากำลังคนที่มีความเชี่ยวชาญเฉพาะทางด้านการออกแบบวงจรไมโครอิเล็กทรอนิกส์ ตั้งแต่ระดับพื้นฐานจนถึงระดับสูง เพื่อรองรับการเติบโตของอุตสาหกรรมภายในประเทศ อีกทั้งยังมุ่งเน้นส่งเสริมการถ่ายทอดองค์ความรู้และเทคโนโลยีจากผู้เชี่ยวชาญไปสู่บุคลากรรุ่นใหม่ เพื่อสร้างความต่อเนื่องในการพัฒนาอุตสาหกรรมไมโครอิเล็กทรอนิกส์ของประเทศ เพื่อสร้างเครือข่ายผู้เชี่ยวชาญทางด้านการออกแบบไมโครอิเล็กทรอนิกส์ และผู้เกี่ยวข้องในอุตสาหกรรมไมโครอิเล็กทรอนิกส์ ทั้งภาครัฐ และภาคเอกชน

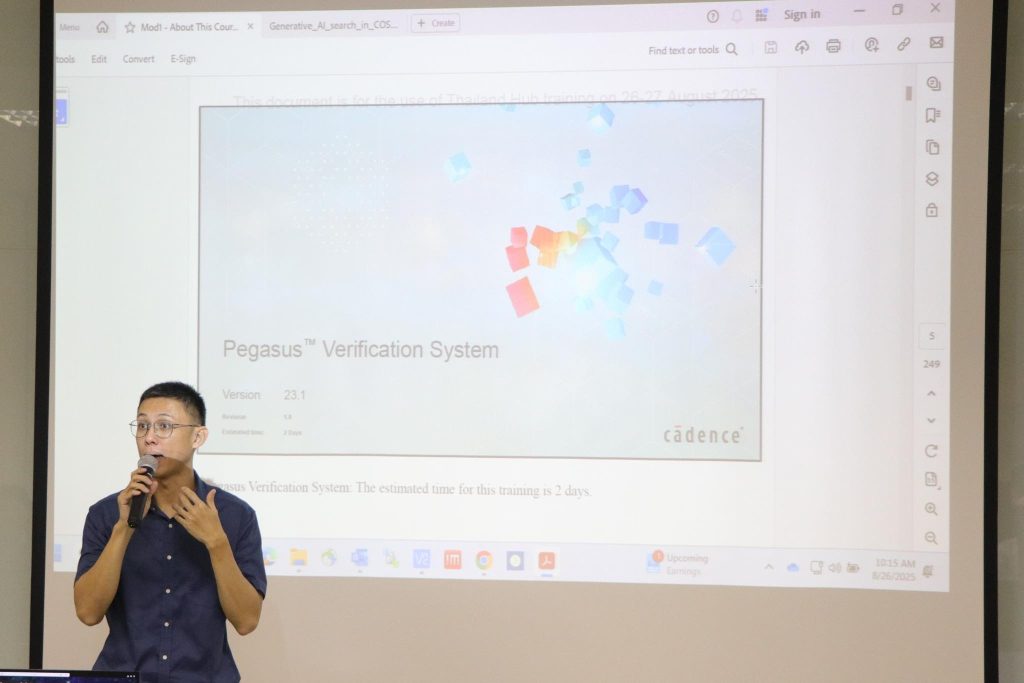

โดยการจัดอบรมครั้งนี้ จัดขึ้นระหว่างวันที่ 26 – 28 สิงหาคม 2568 มีนักวิจัย คณาจารย์ ผู้ประกอบการ เข้ารับการฝึกอบรม จำนวน 54 คน จาก 27 หน่วยงาน ซึ่งจะมุ่งเน้นให้ผู้เข้าร่วมอบรมได้เรียนรู้การออกแบบวงจรรวม ตั้งแต่การทำความเข้าใจกับเครื่องมือออกแบบเวอร์ชันล่าสุด การฝึกปฏิบัติจริง ไปจนถึงการตรวจสอบ Layout และการทำ Parasitic Extraction ซึ่งได้รับเกียรติจากวิทยากรผู้เชี่ยวชาญ Mr. Wan Tat Hooi จากCadence Design Systems, Inc. บรรยายหัวข้อสำคัญ ได้แก่ Pegasus Introduction + Virtuoso version 23.1, Layout Versus Schematic, Quantus Introduction and overview และ Quantus Transistor level Parasitic Extraction